半桥SiC模块并联应用工程实践指南与短路过流2LTO两级关断保护驱动设计深度研究报告

BMF540R12MZA3半桥SiC模块并联应用工程实践指南与短路过流2LTO两级关断保护驱动设计深度研究报告

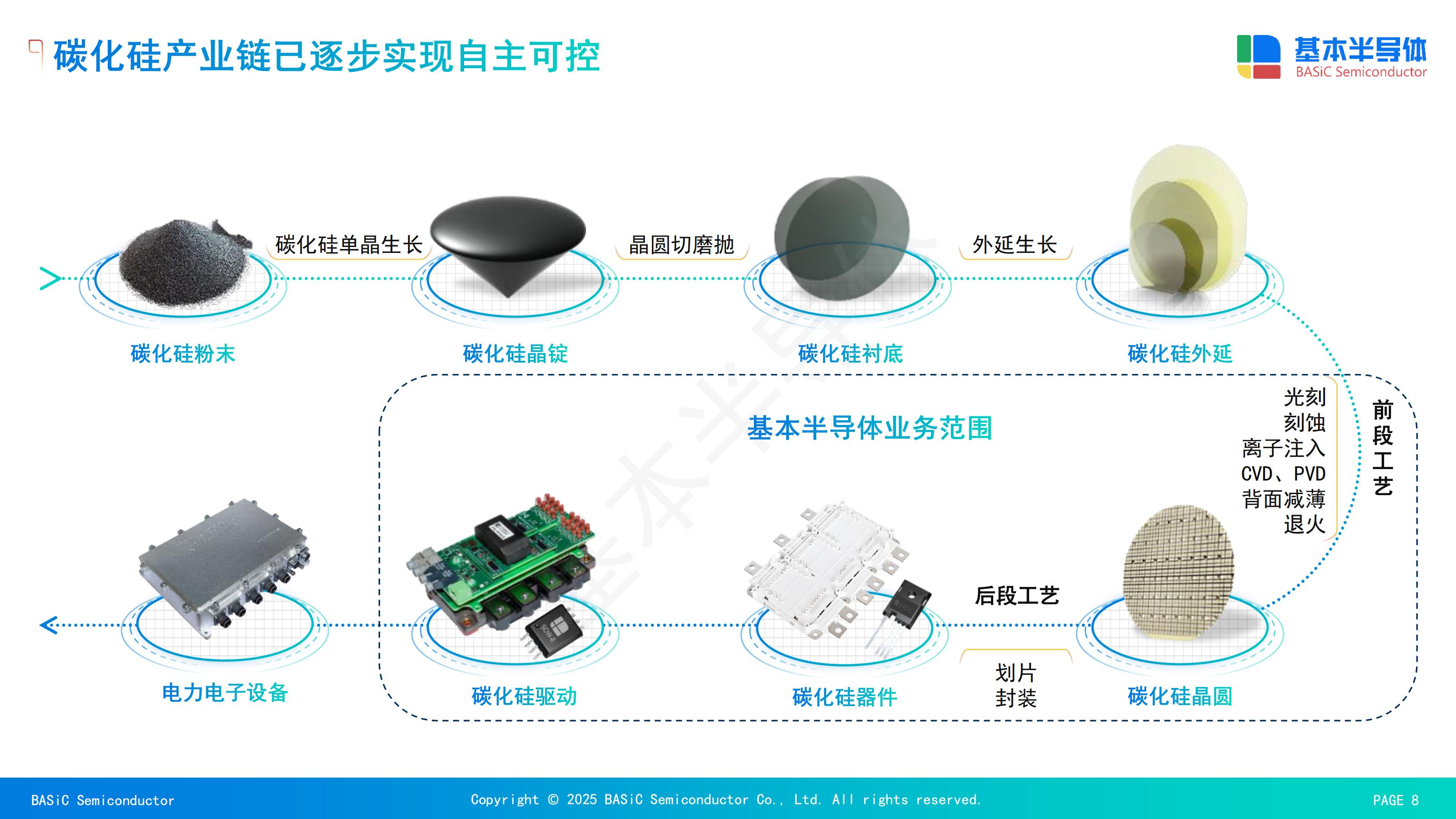

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 绪论:碳化硅功率模块的应用挑战与工程背景

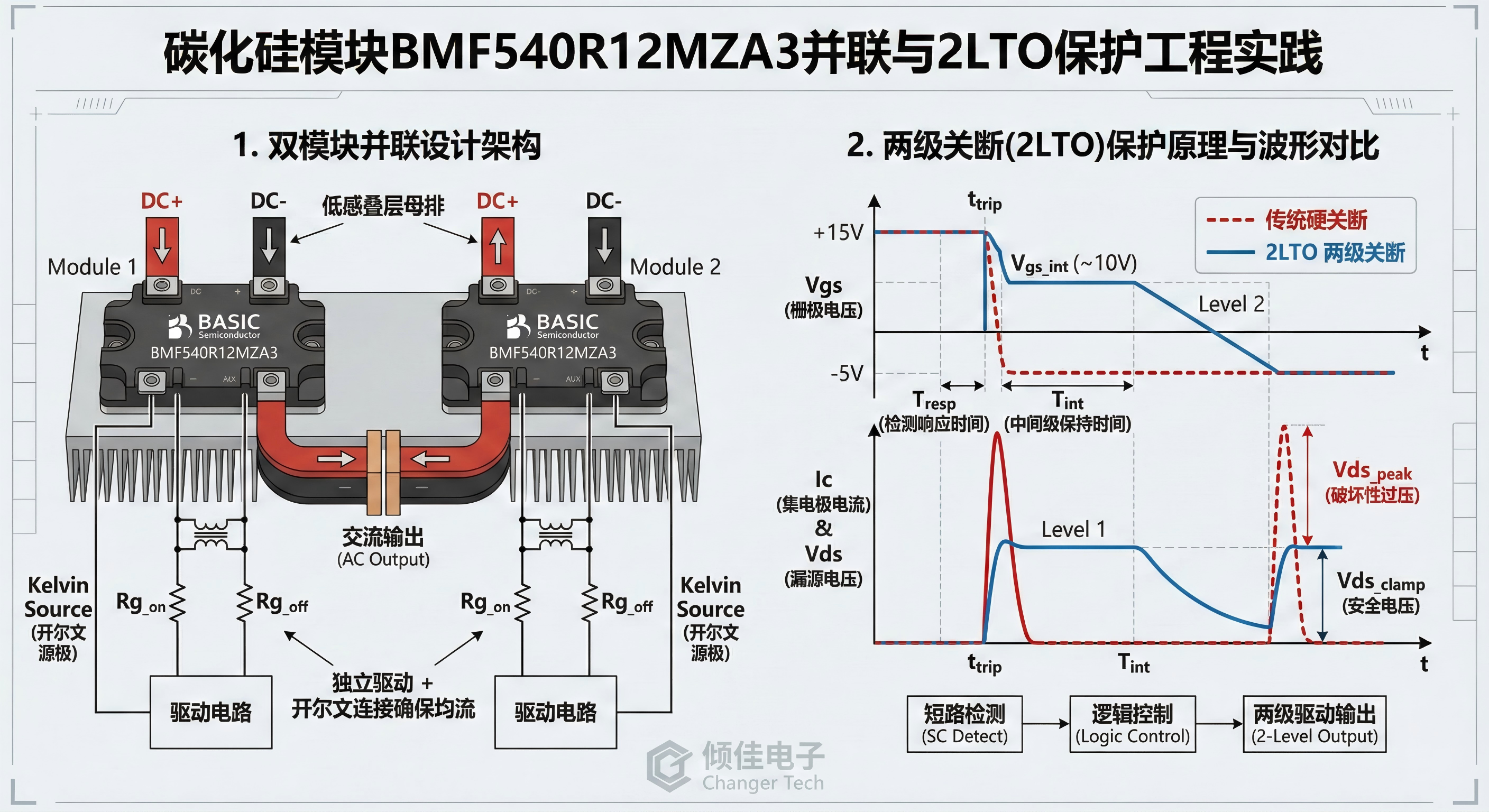

随着电力电子技术向高频、高压、高功率密度方向的迅猛发展,碳化硅(Silicon Carbide, SiC)金属氧化物半导体场效应晶体管(MOSFET)正逐渐取代传统的硅基IGBT,成为固态变压器SST、储能变流器PCS、Hybrid inverter混合逆变器、户储、工商业储能PCS、构网型储能PCS、集中式大储PCS、商用车电驱动、矿卡电驱动、光伏储能变流器以及固态变压器等核心装备的首选功率器件。深圳基本半导体有限公司(BASIC Semiconductor)推出的BMF540R12MZA3是一款采用Pcore™2封装(兼容业界标准EconoDUAL)的1200V、540A半桥SiC MOSFET模块 。该模块凭借其低导通电阻(典型值2.2 mΩ)、低开关损耗以及优异的反向恢复特性,在大功率应用中展现出巨大的潜力。

然而,单模块的电流能力往往难以满足兆瓦级系统的需求,多模块并联(Paralleling)成为扩展功率容量的必由之路。与此同时,SiC MOSFET芯片面积小、电流密度极高,导致其短路耐受时间(Short Circuit Withstand Time, SCWT)显著短于传统IGBT(通常仅为2-3 μs vs. IGBT的10 μs)2。且SiC器件开关速度极快(di/dt > 5 kA/μs),在短路关断过程中极易感应出破坏性的过电压尖峰。因此,传统的硬关断(Hard Turn-Off)保护策略已不再适用,必须引入**两级关断(Two-Level Turn-Off, 2LTO)**技术以平衡保护速度与电压应力。

倾佳电子为电力电子工程师提供一份详尽的工程实践指南,深入剖析BMF540R12MZA3模块的并联设计原则与2LTO保护驱动电路的参数化设计方法。将结合器件物理特性、封装寄生参数模型及电路仿真理论,提供从原理分析到工程落地的全方位指导。

2. BMF540R12MZA3模块特性深度解析及其工程影响

工程设计的起点是对核心器件特性的透彻理解。BMF540R12MZA3的电气参数不仅决定了单管的性能,更直接约束了并联系统的均流策略和保护电路的响应速度。

2.1 静态特性与并联均流的物理基础

在并联应用中,静态均流主要取决于器件的导通电阻(RDS(on))和阈值电压(VGS(th))的一致性及其温度特性。

2.1.1 导通电阻的温度系数效应

根据数据手册,BMF540R12MZA3在结温Tvj=25∘C且驱动电压VGS=18V时,典型导通电阻为2.2 mΩ;而在Tvj=175∘C时,该值上升至3.8 mΩ 。

这一显著的**正温度系数(Positive Temperature Coefficient, PTC)**是MOSFET并联应用的天然优势。当并在联阵列中的某一模块因电流分配过多而温度升高时,其RDS(on)会随之增大,迫使电流自动向温度较低(电阻较小)的其他模块转移。这种自平衡机制在很大程度上抑制了静态热失控的风险 。相比之下,IGBT在低电流密度下往往表现出负温度系数(NTC),极易导致并联失稳。

工程启示: 尽管PTC效应有助于均流,但2.2 mΩ的超低电阻值意味着外部连接回路(母排、端子)的电阻占比显著增加。如果母排设计不对称导致连接电阻偏差达到0.2 mΩ(即模块电阻的10%),就会抵消器件自身的均流能力。因此,并联系统的机械对称性设计至关重要。

2.1.2 阈值电压离散性与动态失配

数据手册显示,BMF540R12MZA3的栅极阈值电压VGS(th)分布范围为2.3V(最小值)至3.5V(最大值) ,典型值为2.7V 。

这1.2V的离散度在并联应用中是巨大的挑战。在动态开关过程中,尤其是在开通瞬间,VGS(th)较低的模块会率先导通,并在米勒平台建立之前承担大部分负载电流。同理,在关断过程中,该模块会最后关断。这种瞬态的电流过载(Dynamic Current Overstress)虽然持续时间短(纳秒级),但在高频开关下会造成该模块过热,甚至因瞬态功耗超出SOA(安全工作区)而导致失效 。

工程对策:

筛选与配对(Binning): 在批量生产中,建议对模块进行VGS(th)分档,确保并联组内的阈值电压偏差控制在0.2V以内 。

独立栅极电阻: 必须为每个并联模块配置独立的栅极电阻,利用电阻的压降来补偿阈值电压的差异,抑制动态环流。

2.2 动态特性与封装寄生参数

BMF540R12MZA3采用Pcore™2封装,内部集成氮化硅(Si3N4)AMB陶瓷基板,具有优异的散热和绝缘性能 1。

输入电容(Ciss): 典型值为33.6 nF (VDS=800V) 。

总栅极电荷(QG): 典型值为1320 nC 。

内部栅极电阻(RG(int)): 1.95 Ω 。

驱动功率挑战:

若将4个模块并联,等效Ciss将高达134.4 nF,总QG达到5280 nC。假设开关频率为20 kHz,驱动电压摆幅ΔVGS=23V (+18V/-5V),则驱动功率需求为:

Pdrive=QG,total×ΔVGS×fsw=5.28μC×20kHz≈0.1W

虽然平均功率不高,但瞬态峰值电流需求极大。为了保证开关速度(例如ton≈100ns),驱动器必须能够提供瞬时大电流:

Ipeak≈tonQG,total=100ns5.28μC≈52.8A

这表明,常规的单芯片驱动器(如4A或6A输出)完全无法直接驱动并联模组,必须采用推挽放大级(Booster Stage)或大功率驱动核 。

2.3 SiC短路耐受能力的物理极限

与硅IGBT相比,SiC MOSFET的短路耐受能力是其“阿喀琉斯之踵”。BMF540R12MZA3的数据手册未明确给出SCWT值,但依据同类1200V SiC产品的物理特性分析:

极高的饱和电流密度: SiC MOSFET的短沟道设计使其跨导(gm)较高,短路时的饱和电流可能达到额定电流的10倍以上(即>5000A)。

有限的热容: SiC芯片面积通常仅为同电流等级IGBT的1/3至1/4,导致短路瞬间产生的焦耳热无法迅速扩散,结温急剧上升。

失效机理: 当结温超过铝电极的熔点(约660°C)时,栅极氧化层会因热应力破裂或源极金属层熔化导致器件永久失效。

业界普遍认为,1200V SiC MOSFET的SCWT限制在2 μs至3 μs之间 2。这意味着保护电路必须在检测到短路后的1.5 μs内完成关断动作,这对检测电路的带宽和抗干扰能力提出了极高要求。

3. BMF540R12MZA3并联应用工程实践指南

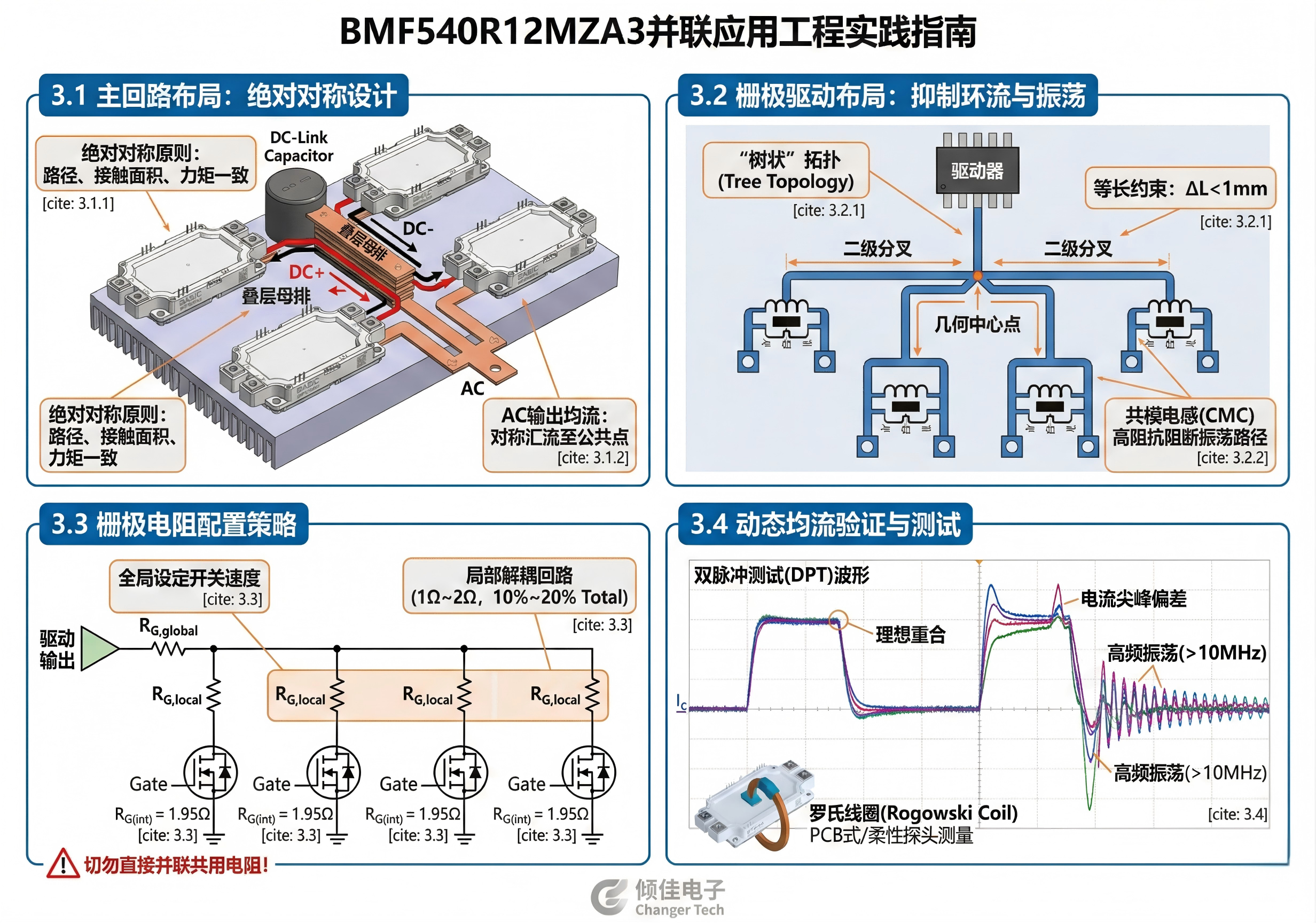

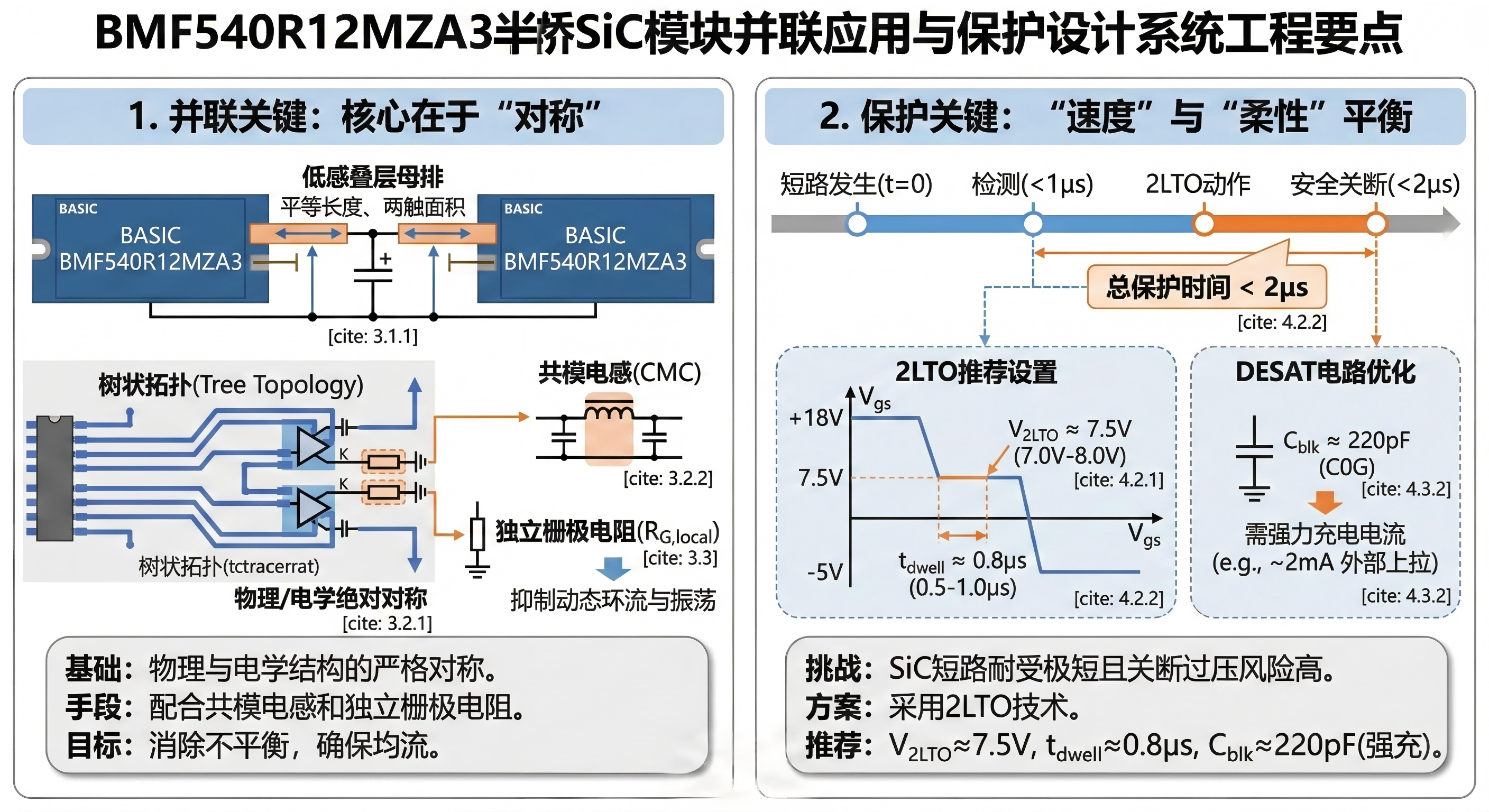

并联设计的核心目标是消除不平衡。本章节从主回路设计、栅极驱动布局以及磁性元件应用三个维度,详细阐述实现“完美对称”的工程方法。

3.1 主回路(Power Loop)布局设计

对于RDS(on)仅为2.2 mΩ的模块,母排的寄生电阻和电感主导了均流效果。

3.1.1 叠层母排与对称性设计

必须采用低感叠层母排(Laminated Busbar),利用平行板电容效应抵消寄生电感。

绝对对称原则: 从直流支撑电容组(DC-Link Capacitors)到每个并联模块的物理路径长度必须严格一致。这不仅包括正负极母排的长度,还包括连接螺栓的接触面积和拧紧力矩 。

星形连接(Star Connection): 推荐采用放射状的星形连接方式,将电容组汇流点置于几何中心,各分支母排等长延伸至模块端子。避免采用“菊花链”(Daisy Chain)连接,因为链首模块会承受最高的电压应力和纹波电流,导致过早老化 。

3.1.2 交流输出均流

并联模块的交流输出端(AC Output)同样需要对称汇流。如果在交流侧存在阻抗差异,哪怕是微小的电感差异(如10 nH),在数千安培/微秒的di/dt下也会产生显著的感应电压差,阻碍动态均流。建议将所有模块的AC端子通过等长铜排连接到一个公共输出点,再由此点引出至负载或电抗器。

3.2 栅极驱动回路布局:抑制环流与振荡

栅极回路是并联系统中最敏感的部分。由于各模块源极(Source/Kelvin Emitter)在功率侧相连,在驱动侧也相连,形成了一个极易感应出差模噪声的接地环路。

3.2.1 “树状”拓扑(Tree Topology)

驱动信号的PCB走线必须遵循严格的“树状”分叉结构 。

一级分叉: 从驱动器输出级引出主干线。

二级分叉: 在几何中心点分叉,分别连接到各个模块。

等长约束: 必须保证从分叉点到每个模块栅极插针的PCB走线长度误差小于1mm。这能确保栅极信号的传输延迟偏差(Skew)控制在纳秒级别。

3.2.2 共模电感(Common Mode Choke)的应用

即便布局完全对称,器件内部参数的微小差异仍可能导致开关速度不同步,进而在并联模块的辅助源极之间产生高频环流(Circulating Current)。这种环流会通过源极电感反馈到栅极电压上,引发高频振荡(Oscillation)。

工程建议: 在每个模块的栅极(Gate)和辅助源极(Auxiliary Source)回路中串联一个共模电感。

选型指南: 选择漏感极小、但共模阻抗较高的磁环(如铁氧体磁珠或专门的信号共模电感)。该电感对正常的驱动电流(流进栅极、流出源极,为差模信号)呈现低阻抗,不影响驱动速度;但对模块间的环流(在源极连线间流动)呈现高阻抗,从而有效阻断振荡路径 。

3.3 栅极电阻配置策略

切勿将多个模块的栅极直接并联后共用一个栅极电阻,这必然导致严重的振荡。

全局电阻(RG,global)与局部电阻(RG,local):

RG,global: 放置在驱动器输出端,用于设定整体的开关速度(di/dt和dv/dt)。

RG,local: 紧靠每个模块的栅极管脚放置,用于解耦各模块的栅极回路,抑制LC振荡。

阻值分配: 经验法则建议,RG,local应至少占总电阻的10%~20% ,或者取值为1Ω~5Ω。对于BMF540R12MZA3,其内部已有1.95Ω电阻,外部局部电阻可取1Ω-2Ω,全局电阻根据总驱动电流能力进行计算 。

3.4 动态均流的验证与测试

在工程实施阶段,必须通过**双脉冲测试(Double Pulse Test, DPT)**验证均流效果。

罗氏线圈(Rogowski Coil)测量: 在每个模块的源极或漏极套入罗氏线圈。由于Pcore™2模块端子紧凑,建议使用PCB式罗氏线圈或超薄柔性探头。

评估指标: 观察开通和关断瞬间的电流波形重合度。如果发现某模块电流尖峰明显高于其他模块,需检查该模块对应的PCB走线长度、过孔数量以及栅极电阻的一致性。同时,需监测栅极电压波形,确保无明显的高频振荡(>10MHz)。

4. 基于2LTO的短路保护驱动设计指南

鉴于SiC MOSFET短路耐受时间极短且关断过压风险高,采用**去饱和检测(Desaturation Detection, DESAT)配合两级关断(2LTO)**是目前业界公认的最佳保护方案。

4.1 2LTO保护机制与工作原理

2LTO的核心思想是“先限流,后关断”。当检测到短路时,驱动器不立即完全关断器件,而是先将栅极电压从+18V降低到一个中间电平(Intermediate Voltage, V2LTO)。

第一阶段(降压限流): 栅极电压降至V2LTO。此时MOSFET从深线性区(Deep Triode Region)进入饱和区(Saturation Region),沟道电阻增大,漏极电流被限制在一个较低的水平(例如2-3倍额定电流),而不是短路峰值电流。

驻留阶段(Dwell Time): 保持V2LTO一段时间(tdwell),让电路中的杂散电感能量部分释放,同时等待电流稳定。

第二阶段(完全关断): 栅极电压拉低至-5V,彻底关断器件。由于此时切断的电流已大幅降低,因此产生的VDS过冲(Vspike=Lσ⋅di/dt)被显著抑制,确保器件在安全工作区(SOA)内关断 。

4.2 关键参数设计与计算

4.2.1 中间电平 V2LTO 的选取

V2LTO的选择是2LTO设计的核心。选得太高,限流效果不明显,器件仍承受巨大热冲击;选得太低,第一级关断的di/dt过大,导致第一级过压击穿器件。

依据转移特性: 参考同类1200V SiC MOSFET的转移特性曲线(Transfer Characteristics),我们需要找到一个栅极电压,使其对应的饱和电流约为额定电流(540A)的1.5倍至2.5倍。

数据估算: BMF540R12MZA3的阈值电压典型值为2.7V。在VGS=18V时,电流能力远超1000A。通常,SiC MOSFET的米勒平台电压在高电流下约为6V-9V。

推荐值: 建议将V2LTO设定在7.0V 至 8.0V之间。

在7.5V左右,器件通常能维持约800A-1200A的饱和电流。这个电流水平既能被模块短时间耐受,又能显著降低关断时的di/dt 。

调试方法: 在实际台架测试中,从9V开始逐步降低V2LTO,观测短路关断时的VDS尖峰。找到一个电压点,使得第一级关断尖峰与第二级关断尖峰幅值大致相等,此时为最优设置。

4.2.2 驻留时间 tdwell 的设定

原则: tdwell必须足够长,以确保电流稳定并消除振荡;但又必须足够短,以保证总短路持续时间不超过SCWT(2-3 μs)。

推荐值: 设定为0.5 μs 至 1.0 μs。

时序计算:

故障检测与响应延迟(tdetect):约 1.0 μs。

2LTO 驻留时间(tdwell):0.8 μs。

最终关断时间(toff):0.2 μs。

总短路时间: 1.0+0.8+0.2=2.0μs。这刚好卡在安全边界内,留有极小的裕量 。

4.3 DESAT检测电路参数化设计

DESAT电路的响应速度直接决定了系统的安全性。目标是在短路发生后1 μs内触发保护。

4.3.1 DESAT阈值电压 Vdesat_th

SiC特性: SiC MOSFET输出特性为线性,没有IGBT的VCE(sat)拐点。在540A时,VDS=540A×2.2mΩ≈1.2V(25°C)。高温下(175°C)约为2.1V。

设定建议: 设定阈值为6.0V 至 7.0V。这远高于正常导通压降,提供了充足的抗干扰裕量,同时能确保在发生短路(VDS迅速上升至母线电压)时被迅速检测 。

4.3.2 消隐电容 Cblk 与充电电流 Ichg

消隐时间(Blanking Time, tblk)用于屏蔽开通瞬间的噪声,防止误触发。

公式: tblk=IchgCblk×Vdesat_th

设计目标: tblk≈0.8μs(极为激进,但对SiC是必须的)。

典型参数: 多数驱动芯片(如基本半导体BTD5350或TI UCC217xx)内部电流源Ichg约为250μA - 500μA。

计算:

Cblk=6.5V500μA×0.8μs≈61pF

工程隐患: 61 pF的电容过小,极易受PCB寄生电容影响导致时间漂移或抗噪能力不足。

改进方案: 必须使用外部上拉电阻或选择支持更大充电电流的驱动器。若通过外部电阻将充电电流提升至2 mA,则:

Cblk=6.5V2mA×0.8μs≈246pF

使用220 pF 或 270 pF的C0G材质电容是更为稳健的工程选择 。

4.3.3 检测二极管选型

DESAT二极管承受着全母线电压(1200V)。必须选用低结电容、超快恢复的高压二极管。

推荐: 使用串联的两只1200V/1A SiC肖特基二极管。SiC二极管无反向恢复电流,能显著减小对检测电容的误充电,提高检测精度和抗噪性。

5. 驱动器硬件实现与PCB Layout规范

基于上述理论,本节给出基于基本半导体驱动芯片的具体实现方案。

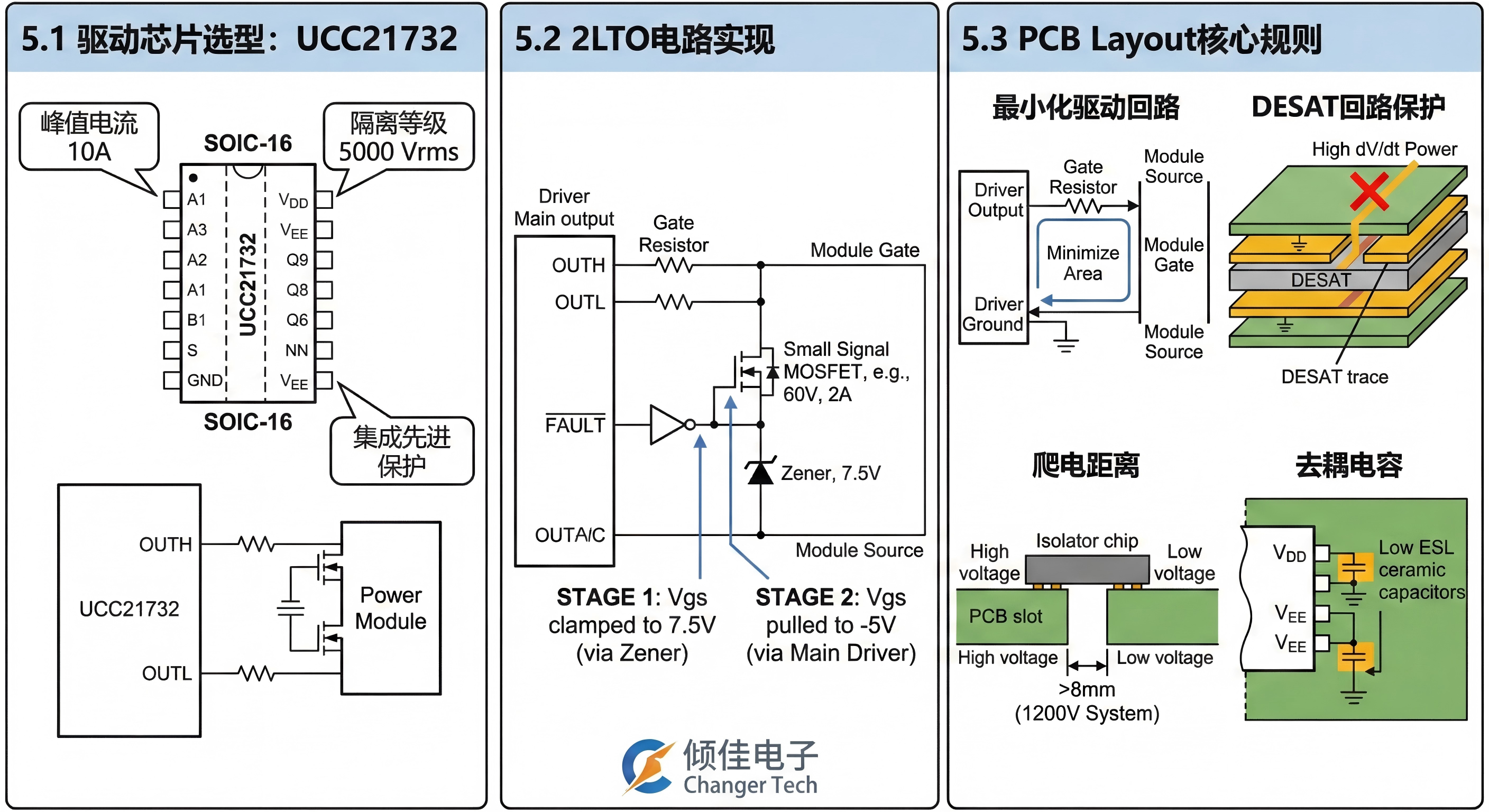

5.1 驱动芯片选型:UCC21732

UCC21732 的核心优势在于将高驱动电流、高可靠性隔离与先进保护集成在单个 SOIC-16 封装内。

驱动能力: 峰值电流10A,足以驱动并联后的高栅极电荷,无需额外的推挽缓冲级(在2并联以内)。

隔离等级: 5000 Vrms,满足1200V系统的安规要求。

5.2 2LTO电路实现

若选用的驱动芯片未内置可编程的2LTO功能(如仅支持软关断STO),则需搭建分立的2LTO网络:

电路构成: 在栅极(Gate)与源极(Source)之间并联一条由小信号MOSFET(如60V, 2A)和稳压二极管(Zener, 7.5V)串联组成的支路。

逻辑控制: 利用驱动芯片的FAULT开漏输出信号。当FAULT拉低(检测到短路)时,通过逻辑反相器迅速导通小信号MOSFET。

动作过程: 小MOSFET导通后,将栅极电压强行钳位在稳压二极管电压(7.5V)上,实现第一级关断。经过驱动器内部设定的延迟后,主驱动输出拉低至-5V,完成第二级关断。

5.3 PCB Layout核心规则

对于SiC驱动板,Layout决定了成败。

最小化驱动回路: 驱动器输出-栅极电阻-模块栅极-模块源极-驱动器地,此回路包围的面积必须做到最小。建议采用多层板设计,驱动信号层与地层紧密耦合,利用层间电容抵消寄生电感 。

DESAT回路保护: DESAT检测线是高阻抗敏感线。必须远离高dV/dt的功率走线(如动点)。如果在多层板上,DESAT走线上下层应有地平面屏蔽。

爬电距离(Creepage): 在驱动芯片下方和高压侧电路周围,必须保证足够的爬电距离(1200V系统通常要求>8mm)。必要时在PCB上开槽(Slotting)。

去耦电容: 驱动电源(VDD/VEE)的去耦电容应紧贴驱动芯片管脚放置,优先选用低ESL的陶瓷电容。

6. 总结与建议

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,BASiC基本半导体SiC碳化硅MOSFET功率模块,BASiC基本半导体SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

BMF540R12MZA3半桥SiC模块的并联应用与保护设计是一项系统工程,容不得半点粗糙。

并联关键: 核心在于**“对称”**。物理结构的对称(母排、PCB走线)是电学对称的基础。配合共模电感和独立栅极电阻,可以有效抑制动态环流和振荡。

保护关键: 核心在于**“速度”与“柔性”的平衡**。必须在2 μs内做出反应,但关断过程又不能过猛。2LTO是解决这一矛盾的唯一解。推荐设置: V2LTO≈7.5V , tdwell≈0.8μs ,配合**Cblk≈220pF**(需强力充电电流)的DESAT电路。

工程参数推荐表

| 参数项 | 推荐值/策略 | 备注 |

|---|---|---|

| 驱动电压 | +18V / -5V | 负压关断是必须的,防止误导通 |

| 栅极电阻 | 全局 RG + 局部 RG (1Ω-5Ω) | 局部电阻抑制并联振荡 |

| 驱动峰值电流 | > 10A (每模块) | 并联时需按比例增加 |

| DESAT阈值 | 6.0V - 7.0V | 兼顾抗噪与响应速度 |

| 消隐时间 tblk | 0.8 μs - 1.2 μs | 必须 < 1.5 μs 以保证安全 |

| 2LTO 中间电压 | 7.0V - 8.0V | 限制短路电流至2-3倍额定值 |

| 2LTO 驻留时间 | 0.5 μs - 1.0 μs | 耗散杂散能量,抑制过压 |

| PCB布局 | 夹层板(Mezzanine)+ 树状走线 | 确保零Skew,实现完美同步 |

通过严格遵循本指南中的设计规范,工程团队可以充分释放BMF540R12MZA3模块的高功率密度优势,构建出既高效又可靠的下一代碳化硅电力电子系统。

2026-02-04 11:58:36

目录 返回

首页